Coursera: Introduction to FPGA Design for Embedded Systems

コロラド大学ボルダー校のTimothy Scherr先生による組み込みシステム向けFPGA設計入門の4週間コースをCourseraで受講しました。

そもそもFPGAに関しては全くの初心者(電子回路とか論理回路については素人とまでは言わないけれど)で、中級者向けのこのコースについていけるのかは未知数でしたが、論理回路に関するなけなしの知識を総動員して最終週までたどり着けました。

Quizは満点が出るまでやり直して、無事100%で修了できました。(1/24)

受講の動機

去年の秋からCourseraの専門講義 deeplearning.ai を受講していて、第5講の開講が延期になって1ヶ月空いたので何か受けようかなと思ったのと、とある社内プロジェクトでFPGAをいじることになったのとで受講を決めました。

概要

実際に手を動かしながら、FPGA開発の基礎を四週間で習得します。

・プログラマブル・ロジック・デバイスの歴史

・FPGAの選び方(各社のFPGAの特長やFPGAのアーキテクチャの違い)

・開発環境の使い方(インストールから回路設計まで)

・回路設計ハンズオン(加算器からNios II*1を使った組み込みシステムまで)

生徒同士で採点し合うpeer assessmentの仕組みを採用しているコースなので、自動採点のみのコースと違って締め切りが重要になります。(システム的には課題の提出は可能ですが、採点してくれる生徒がいなくなってしまう為)

講義は全て英語で、とてもアメリカっぽい*2英語です。

英語字幕とトランスクリプションはありますが、日本語字幕は(現在のところ)用意されていません。

イントロダクションがスパイ・エージェント養成コースみたいな演出になっています*3が、ビデオを見ながらFPGA開発環境(IntelのQuartus Prime)をインストールして実際に使いながら進めていくハンズオン形式のチュートリアルといった感じでした。ビデオを適宜止めながら画面を操作するので、ビデオの長さ以上の時間がどうしてもかかります。

推奨環境

Quartus Primeの動作環境がWindowsとLinux(RedHatもしくはCentOS)のみで、Macでエミュレータを動かすのは非推奨、と明言されていましたが、残念ながら手元にはMacBookやiPad Proしかないので、仮想化技術で行けるところまで行って、駄目なら駄目でその時考えることにしよう、と思って始めました。

Macでもなんとか最後まで受講できましたが、この講義に関してはWindowsマシンがあるならWindowsでの受講をお薦めします。

メモリは(WindowsにせよLinuxにせよ)8GB以上推奨、とのことです*4。

Linux絡みの注意点

・講義でも使われている設計検証ツールModelSimの無料版は32bit版で、これを64bit環境で動かすのにあれこれ(デフォルトでは入っていないi686なものを)追加インストールする必要がありました。

・IP CatalogのライブラリからIP部品(乗算器、SQRTなど)を調達する時に出てくるMegaWizardが、先に進むごとに重くなって三ページ目ぐらいでフリーズします。これはCentOSのデスクトップ効果(ビジュアルエフェクト)を標準からCompizにするとなぜか直ります。(普通逆かなと思うんだけど)

・回路図でユーザ定義シンボルの右上に余計なテーブルみたいなのが表示されて、小さくはできるけど消し方が分かりませんでした。

macOS上で頑張りたい人のためのメモ

・最初Docker for Macで行けないか試しました。CentOSを入れて、画面はXQuartzに出してインストーラを走らせて、インストール自体は完了しますが起動しようとすると謎ダンプを表示して落ちます。(CentOSのバージョンを色々試したり、Xの画面が出なくて右往左往したりで半日ぐらい格闘してたと思います)。

・その後(Dockerは諦めて)VirtualBoxにCentOS(6.9。依存ライブラリの都合上6.x系推奨)を入れた上で無事動きました。Dockerではハードウェア的な何かをチェックされて落ちたのでしょうか。

・メモリは8GB以上推奨とのことでしたが、3GB強程度の割当てで最後まで行けました。

以下受講記録

Week 1: What's this programmable logic stuff anyway? History and Architecture(〜1/1)

・FPGAに至るまでのプログラマブルな論理回路の歴史。

・加算器と乗算器の話。

課題はQuiz17問とAssignment。(講義の途中にDiscussionといって一問一答がある。成績には関係ないようだけれど)

QuizはPROM、PLA、PAL、CPLD、FPGA、LUT*5、ASSP、ASIC、SoC、みたいな用語と、それぞれの特長とか。

Assignmentは、(1) 2ビットの全加算器の論理式と回路図、(2) 簡単な論理式をPLAで実装した図を描く の2話。

AssignmentはPDFで提出して、peer assessment(生徒同士で採点する仕組み)で採点される。ランダムにあてがわれる他の3人の生徒の採点を担当し、ランダムにあてがわれた他の3人からの採点(のmedian)で自分の点が決まる、という仕組み。

とりあえず満点で通過。

Week 2: FPGA Design Tool Flow; An Example Design (〜1/8)

AlteraのQuartus Prime Development Suite(無料で使えるLite版)のチュートリアル的な週だった。

ビデオに従ってQuartus Primeで回路図を描いて(乗算回路とRAMにクロックやデータ入出力を繋ぐだけの簡単なお仕事)、コンパイルしてFmax(可能な最大クロック周波数)を求めたり、分析してパラメータを変えてコンパイルし直したり、ModelSimというシミュレータでシミュレーションを動かしたりした。

課題はQuiz19問と、Assignmentとして各ビデオ毎に撮ったQuartus Primeのスクリーンショットの提出。

スクリーンショットはpeer assessmentで採点。

今週のハマりどころは

・Quartus Prime(Linux版)をMacで動かすところ

・課題のスクリーンショットの指示に一貫性がない(ビデオの最後で指示される内容と、提出時に求められている内容が違う)

・ModelSimが動かない(無料版は32bitという問題)

・MegaWizardが固まる

なんとか満点で通過。(Quizは全問正解になるまで4回挑戦した*6)。

(1/8: Week 2を終えたところ)

Week 3: FPGA Architectures: SRAM, FLASH, and Anti-fuse (〜1/15)

- 再プログラミング可能かどうか(コンフィギュレーションメモリの種類がFLASHやSRAMか、あるいはAnti-fuseか)

- サイズ、あるいはロジック密度

- 論理ゲートあたりのコスト

- 速度(最大クロック周波数)

- 電力消費(静的・動的)

- I/Oあたりのコスト(I/O密度)

- チップ上のHard IPが利用可能か(メモリ、DSPブロック、トランシーバ等)

- 決定論的なタイミング(実装毎のタイミングが一貫していること)

- 信頼性(FIT rateで測られる)

- 耐久性(可能なプログラミング回数、保持年数)

- 設計とデータのセキュリティ

これに基づいて、Xilinx / Altera / Microsemi*7 / Lattice 各社の主要なCPLD/FGPA製品をデータシートを見ながら解説していく回。

SRAMベースのFPGAは(SRAMが揮発性だから)起動時に数ミリ秒かけて外部(あるいはオンチップのFLASH)から設定を読み込まないといけない(し、リバースエンジニアリングされるリスクも高まる)とか、Anti-fuseベースのFPGAは一度書き込んだら変更できないけれど高セキュリティだとか。

LUTの入力数とその出力(を受けるflip-flop)数の違いで、比較器や全加算器を作るとLUT当たり何ビット出来るか、という観点からの説明。

自分で各製品の比較表を作っておくことをおすすめする。

(よく入門用に使われているMAX10のお手軽感が理解できた)

課題はQuiz16問のみ。(Assignmentなし。Discussionが2つあった)

なんとか満点通過*8。

Week 4: Programmable logic design using schematic entry design tools (〜1/22)

最終週。ビデオの分量が多くて週末Coursera組にはキツイ週だった。

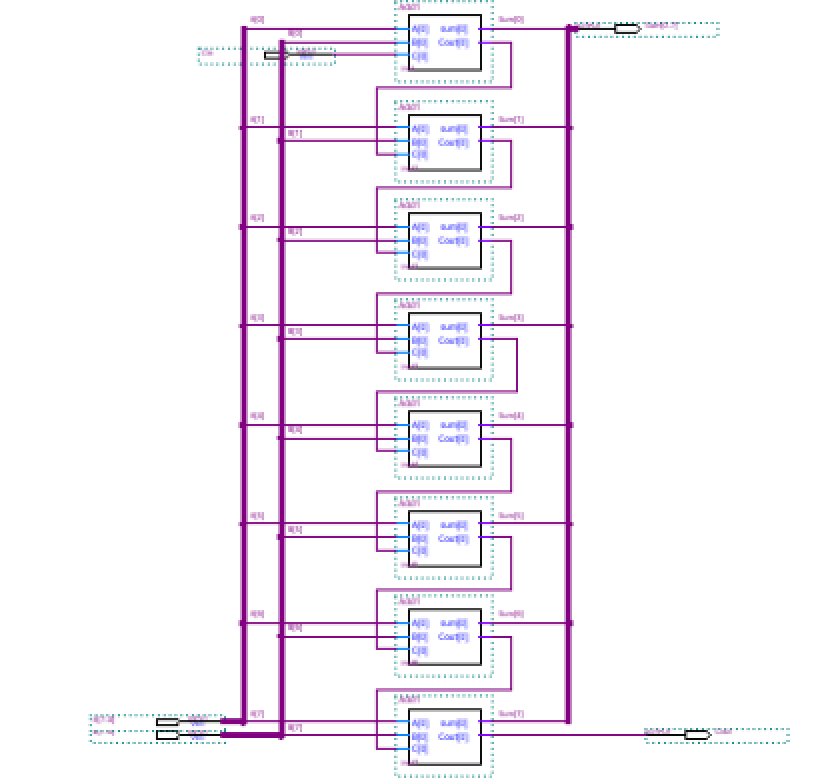

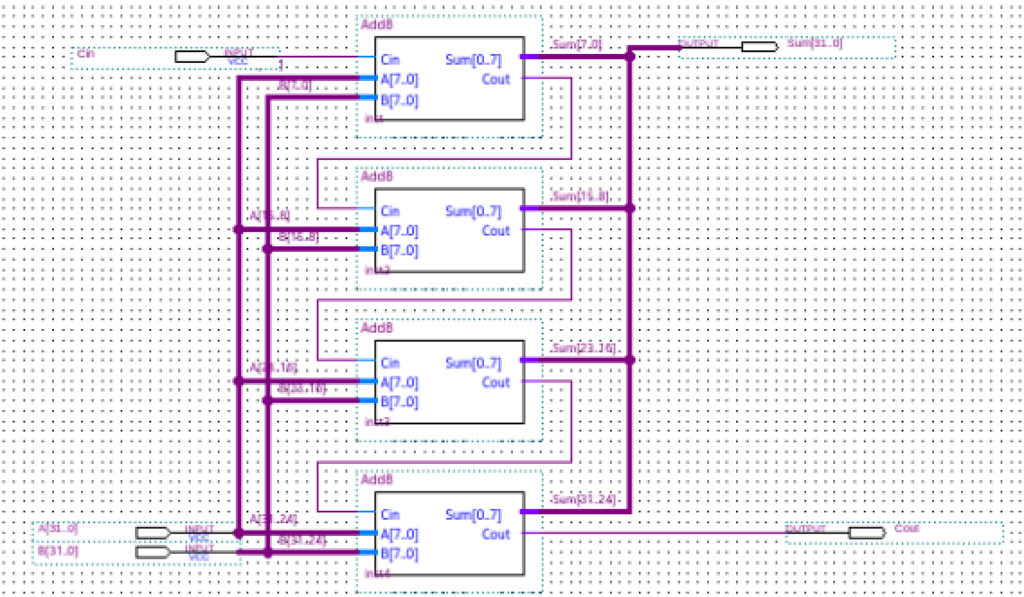

・設計の階層化。1ビットの全加算器を部品化して8個組み合わせて8ビットの加算器を、それを4個組み合わせて32ビットの加算器を作る。

ここに1ビット全加算器があるじゃろ?

( ^ω^)

これをこうして…

( ^ω^)

こうじゃ

( ^ω^)

・既成のIPブロックを利用することで生産性向上(SQRTの計算を例に)

・パイプライン化:時間のかかるロジックにflip-flopを挟んで分割することで、レイテンシは増大するがクロックを上げることができる。データはクロックサイクル毎に1つずつ入っては出ていくのでレイテンシはさほど問題にならない、という話。

・FPGAのI/O(single-ended referenced standards, differential standards)。Differential standards (LVDS, LVPECL) は1シグナルにつきピンを2つ食うが、高速かつノイズ耐性があるのでよく使われるようになった、という話。

・pinの割り当て。グラフィカルなPin Plannerを使う方法と、スプレッドシートライクなAssignment Editorを使う方法と。(他にもSDCファイルをインポートしたりHDLで書いたりTCLスクリプトで自動化したりCADツールでレイアウトしたりと色々ある)

・FPGAへのロジック書き込み(プログラミング)、起動時のロジック読み込み(コンフィギュレーション)の話。

・システム設計ツールQsysを使って組み込みシステムを作ってあなたも伝説のエージェントQになれる?パフォーマンスが最適化されたソフトコアCPUであるNIOS II プロセッサの設計データを利用すれば、一からCPUを設計しなくても良い

・というわけで、ボタン入力4つとLED出力8つを持つだけのシステムをQsysで設計する実習。Verilogをいじって要らない入出力を削除したりとか。

最終週の課題は

・各ビデオ毎に撮ったQuartus Primeのスクリーンショットの提出(peer assessmentで採点)

・32ビット加算器の前後にD-FlipFlopを挟んでFmaxがどれくらい上がるか試せ(回路図とFmax値の提出。peer assessmentで採点)

・Quiz16問

Quizは1投目で77%(一応合格点)、2投目で100%*9取れた。

毎週末に一気にその週のビデオを見て、assignmentをやって、100%が出るまでQuizをやって、という感じだったけれど、4週よく頑張った。

assignmentを2回再提出したせいなのか、最終結果とCertificateが出たのが水曜日。

無事100%で修了できました。

(peer assessmentを待っている間に追加で6人分の採点をしておきました)

*1:IntelのソフトコアCPUで、XilinxでいうところのMicroBlazeに相当。RISCアーキテクチャCPUのFPGA実装。

*3:Week 4でシステム設計ツールQsysを使って組み込みシステムを作る話のところで"By the time you are done, people may mistake you for Q!"って言ってるけどQって何?誰?と思った人。ジェームズ・ボンドのコードネームです。

*4:多分4GBなくても行けますが。

*5:Lookup table。ラッツって言ってた

*6:70%取れれば合格。何度受けてもよくて、最高点が採用されるが、8時間に3回のペースでしか受けられない。1回目80%→2回目95%→3回目95%→4回目100%。毎回ちょっとずつ違う問題だったりするので油断できない。

*7:アメリカ英語だしsemiの発音は「セマイ」

*8:93%→94%→100%

*9:明らかに採点システムが間違ってると思われる部分があって、採点システム側に倒した回答を2投目にしたりとか。Courseraあるある。